对抗知识焦虑,从看懂这条开始

App 下载

台积电绕开3.5亿欧光刻机,推进1.2nm制程

芯片制造工艺|低NA EUV设备|1.2nm制程|High-NA EUV光刻机|台积电|半导体技术|前沿科技

对抗知识焦虑,从看懂这条开始

App 下载

芯片制造工艺|低NA EUV设备|1.2nm制程|High-NA EUV光刻机|台积电|半导体技术|前沿科技

当所有人都以为,芯片制程要突破1.4nm必须依赖那台售价3.5亿欧元的High-NA EUV光刻机时,台积电给了行业一个意外答案。在2026年北美技术论坛上,这家全球最大的晶圆代工厂明确宣布:直到2029年投产的1.2nm、1.3nm制程,都不需要这台“光刻机天花板”。

要知道,单台High-NA EUV的价格,相当于2000辆顶配特斯拉Model 3,还得配套造价不菲的专属厂房和供电系统。台积电到底找到了什么办法,能绕开这台“吞金巨兽”继续推进制程迭代?

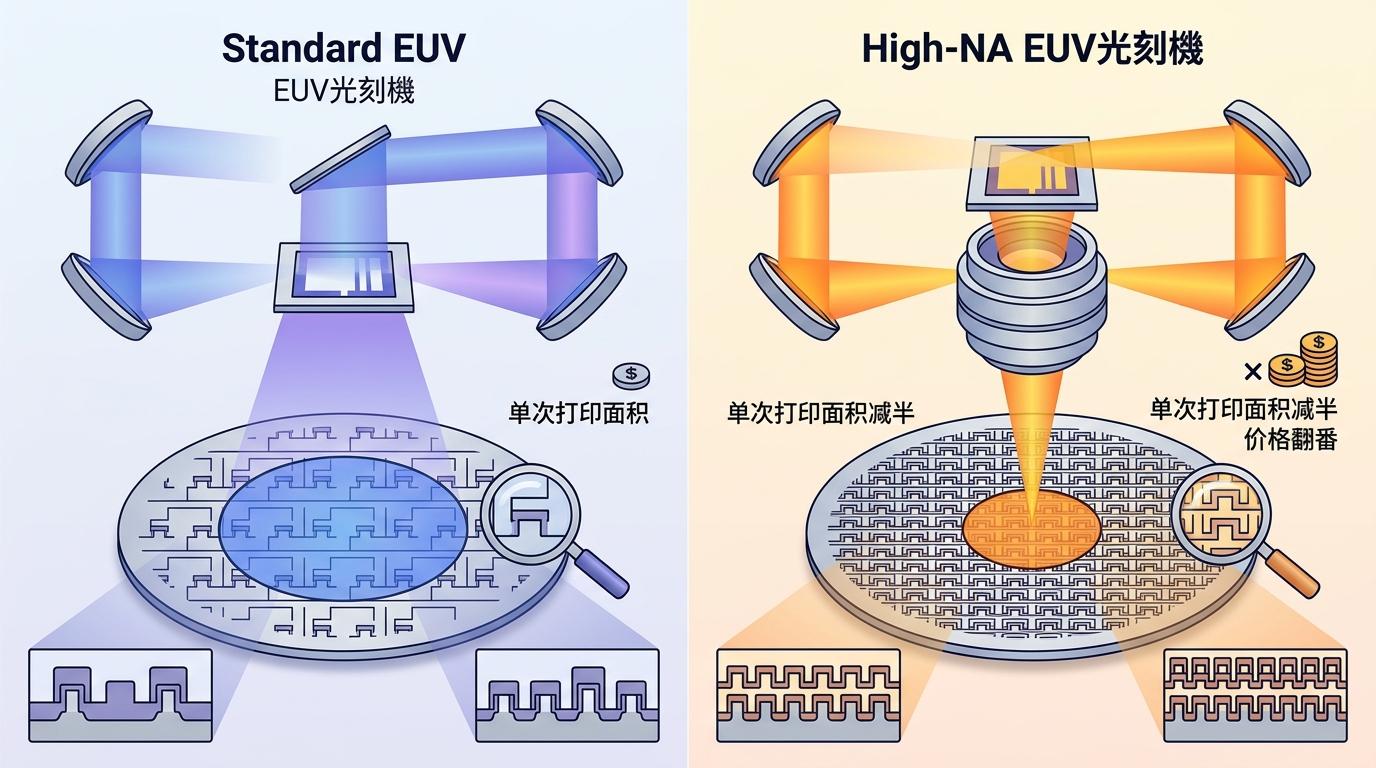

你可以把光刻机想象成一台超级精密的打印机,EUV光刻机就是用13.5纳米波长的极紫外光,在硅片上“印”出晶体管电路。而High-NA EUV相当于升级了打印机的镜头,能把细节印得更细,但代价是价格翻番、单次打印面积减半。

台积电的解法,是把现有低NA EUV的潜力挖到极致。核心武器之一是**设计-技术协同优化(DTCO)**——设计团队和工艺团队从一开始就绑定,不是先做工艺再适配设计,而是同步调整电路布局和光刻参数。比如在A13制程中,他们通过微调晶体管排列和布线规则,让芯片面积直接缩小6%,且设计规则和上一代A14完全兼容,客户不用重新设计IP就能直接升级。

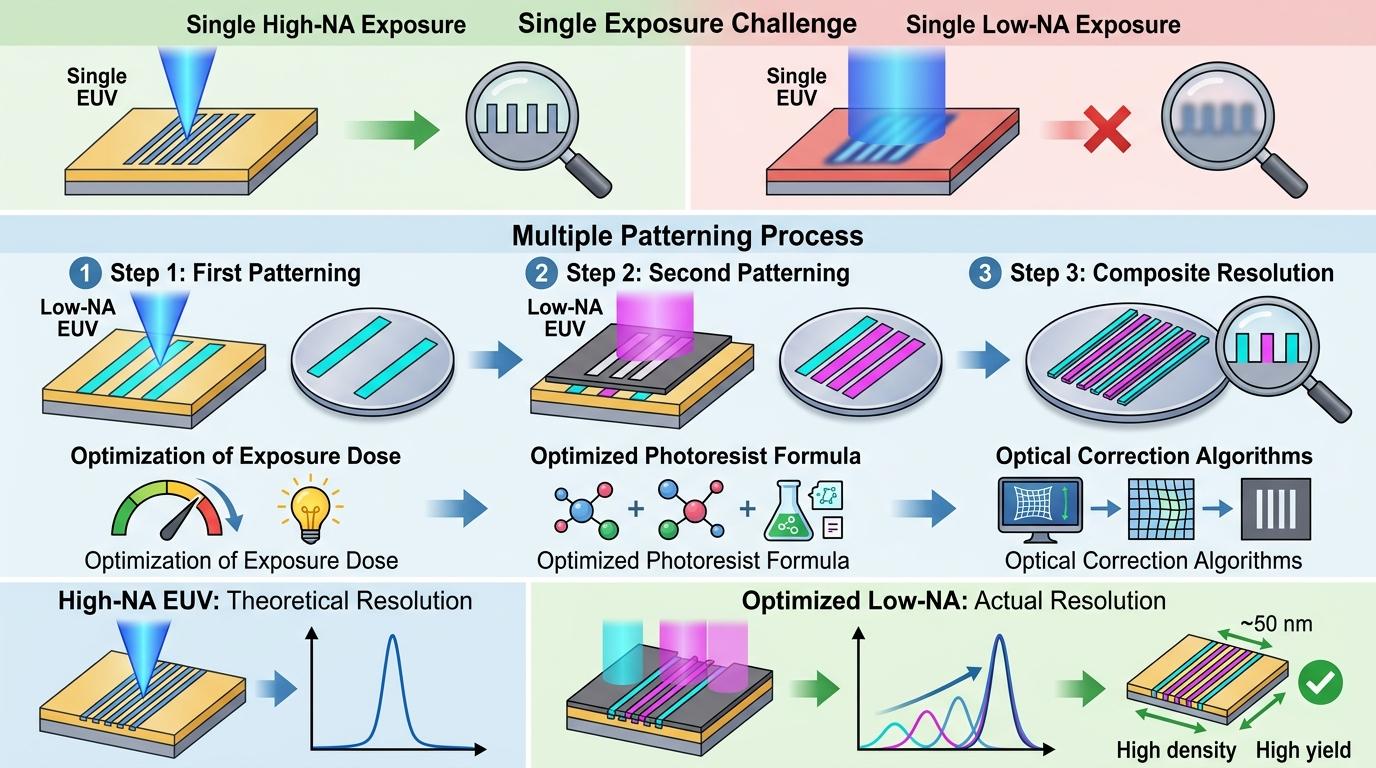

另一项关键技术是**多重曝光与多图案化**。简单说就是用低NA EUV分几次曝光,把原本一次印不出来的精细图案“拼”出来。台积电通过优化曝光剂量、光刻胶配方和光学校正算法,把这种“拼接”的误差控制在纳米级,良率甚至能超过单次曝光。数据显示,这种方法让低NA EUV的实际分辨率,已经摸到了High-NA EUV的理论门槛。

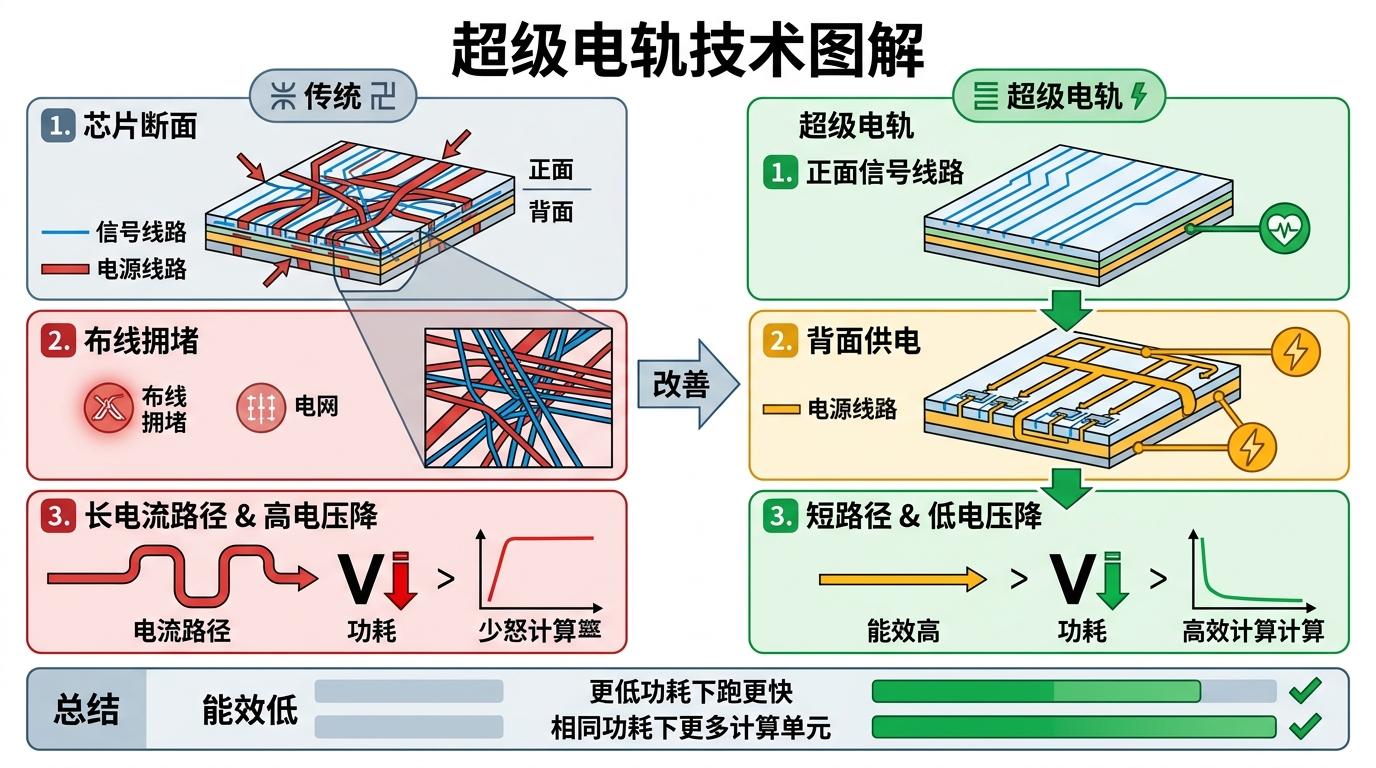

如果说光刻是在硅片上“画画”,那供电就是给这幅画“通电”。传统芯片的电源线路都铺在正面,和信号线路挤在一起,就像在一条马路上同时跑汽车和电线,不仅拥堵还容易漏电。

台积电的破局点,是超级电轨(Super Power Rail)技术——把电源线路移到芯片背面。你可以把它理解成给房子装了“背面电网”,正面只留信号线路,瞬间解决了布线拥堵问题。更关键的是,背面供电让电流路径缩短了90%,电压降(IR drop)直接降低7倍,这意味着芯片能在更低功耗下跑更快,或者在相同功耗下塞更多计算单元。

这项技术首次用在2027年量产的A16制程,到2029年的A12制程会全面普及。台积电的数据显示,采用背面供电后,AI芯片的核心频率能提升6%,功耗降低15%,同时逻辑密度还能再提10%。对需要极致算力的AI和高性能计算来说,这相当于在不升级光刻机的前提下,给芯片“换了个新引擎”。

台积电不是不需要High-NA EUV,而是算清了一笔经济账。

单台3.5亿欧元的设备,加上厂房改造、电力和维护成本,一条High-NA EUV产线的总投入要超过百亿美元。更麻烦的是,High-NA EUV的单次曝光面积只有低NA的一半,产能直接降40%,意味着要达到同样的产量,得买更多设备。对客户来说,还得重新设计芯片适配新的曝光规则,成本至少增加20%。

而台积电现在的路线,能让客户用几乎相同的设计成本,享受制程升级的红利。A13和A14的设计规则完全兼容,客户只要微调布局就能迁移,这对苹果、英伟达等需要大规模量产的客户来说,吸引力远大于那一点点理论上的分辨率提升。

当然,台积电也没放弃High-NA EUV。他们只是把引入时间推迟到2030年之后——那时设备成本会下降,技术会更成熟,客户也做好了设计升级的准备。用台积电高管的话说:“我们不会为了技术而技术,只会在它能带来真正的成本效益时才用。”

当行业都在盯着光刻机的技术参数时,台积电却在“老设备”和“新架构”里找到了更务实的答案。这其实是半导体行业的常态:真正的突破,往往不是来自最昂贵的设备,而是来自对现有技术的极致挖掘,和对行业需求的精准把握。

制程的极限,从来不是光刻机的极限。 当芯片的物理尺寸越来越接近原子级别,真正的竞争会从“谁能印得更细”,转向“谁能把有限的空间用得更聪明”。台积电今天的选择,或许正在定义半导体行业下一个十年的竞争规则——不是比谁的设备更贵,而是比谁的技术更懂客户。